RISC-V & Functional Safety: Why 2026 is the Year of "Open Silicon Sovereignty"

Introduction: The Tipping Point for Open Architecture

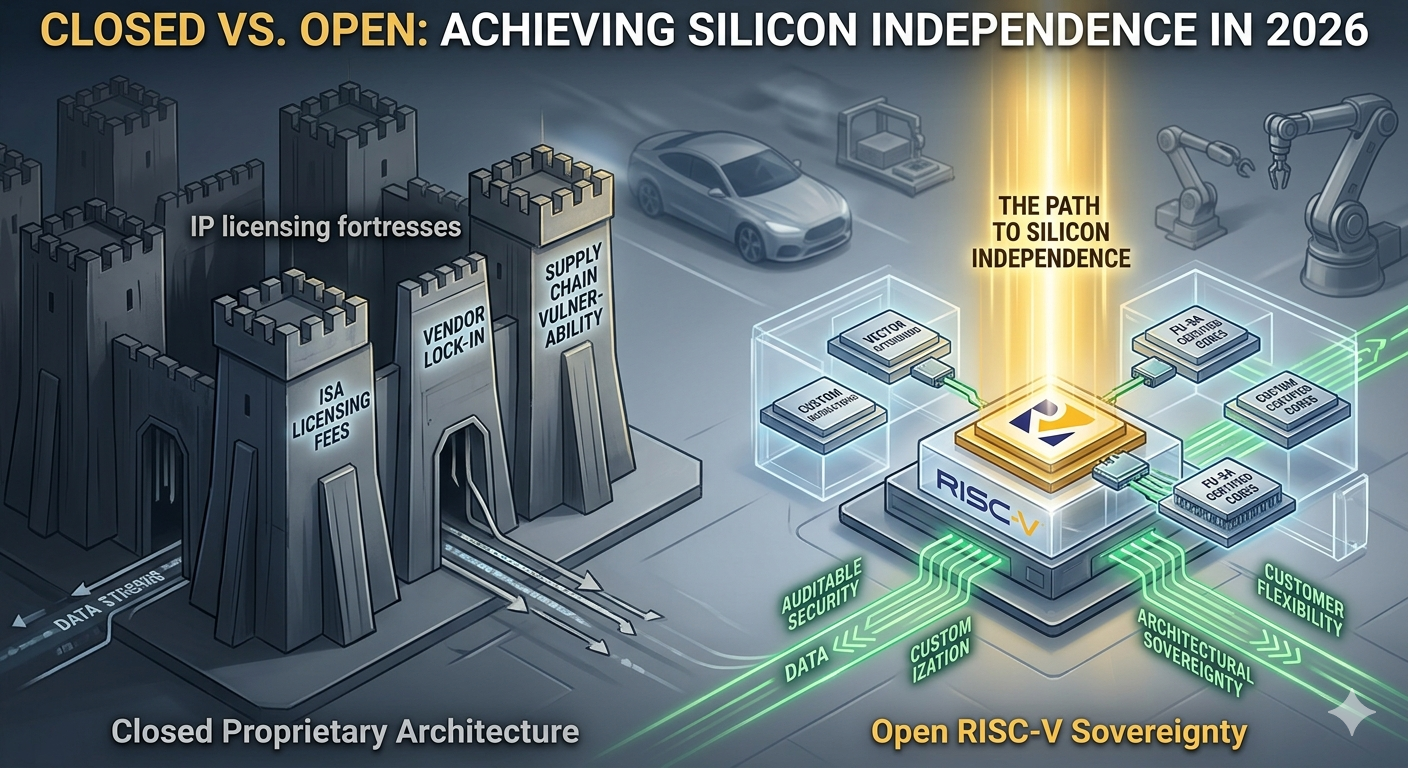

For decades, the embedded world was dominated by a handful of proprietary Instruction Set Architectures (ISAs). If you wanted to build a high-performance industrial controller, you paid the "architecture tax" in licensing fees and locked yourself into a single vendor's roadmap.

In 2026, that landscape has been permanently altered. RISC-V is no longer just an academic curiosity or a hobbyist's playground—it is the gold standard for Mission-Critical Embedded Systems, offering a level of transparency and "Architectural Sovereignty" that proprietary giants simply cannot match.

Achieving ASIL-D and SIL-3: Safety Without Compromise

The most significant breakthrough of the last 24 months has been the mass availability of Functional Safety (FuSa) certified RISC-V cores. Leading silicon providers have now achieved ISO 26262 ASIL-D (Automotive) and IEC 61508 SIL-3 (Industrial) certifications.

1. Dual-Core Lockstep (DCLS) Architecture

Modern RISC-V processors for robotics and automotive braking systems utilize Dual-Core Lockstep.

- How it works: Two identical RISC-V cores execute the exact same instruction stream simultaneously. A hardware-level "comparator" monitors the outputs. If even a single bit differs due to a transient fault (like cosmic ray interference or thermal stress), the system enters a "Safe State" in microseconds.

- The Benefit: This provides the 99.999% reliability required for human-collaborative robots and autonomous logistics vehicles.

2. Vector & Matrix Extensions for Edge AI

Unlike fixed-architecture chips, RISC-V is modular. In 2026, we are seeing the rise of RVV (RISC-V Vector) extensions integrated directly into the main CPU.

- The Innovation: Instead of offloading AI tasks to a power-hungry external NPU, the RISC-V core handles tensor math natively. This reduces data movement energy by up to 40%, allowing high-speed visual inspection and vibration analysis to run on a fraction of the power.

Architectural Sovereignty: A Strategic Business Requirement

Beyond the bits and bytes, the shift to RISC-V is a Business Strategy. In an era of global trade volatility and shifting "Export Controls," relying on a proprietary ISA is a risk.

- Supply Chain Resilience: By using an open ISA, companies can switch between different silicon foundries (like India's SCL or global giants) without rewriting their entire low-level firmware stack.

- Customization: RISC-V allows us at JESilix Solutions to add "Custom Instructions" tailored to specific industrial protocols, creating hardware that is literally built for the task at hand, rather than a "one-size-fits-all" solution.

Why This Matters for Your Projects

Choosing a RISC-V-based solution in 2026 means you are investing in a system that is:

- Auditable: No "black box" security vulnerabilities hidden in proprietary silicon.

- Efficient: Tailored instruction sets mean less wasted clock cycles and lower heat.

- Future-Proof: You own the path of your hardware development, free from external licensing hikes.

Conclusion: Engineering the Future with JESilix

At JESilix Solutions, we believe that the best industrial solutions are built on open, transparent, and high-performance foundations. Our commitment to the RISC-V ecosystem ensures that your automation infrastructure is not just powerful, but sovereign.

SEO Optimization Breakdown

- Primary Keyword: RISC-V Functional Safety 2026

- Secondary Keywords: ASIL-D Certified RISC-V, Dual-Core Lockstep Embedded, Industrial Silicon Sovereignty, RISC-V Vector Extensions, IEC 61508 SIL-3 Hardware.

- Meta Description: Learn why RISC-V has become the 2026 standard for functional safety in automotive and industrial robotics, offering open-source reliability and architectural sovereignty.